### Valparaiso University ValpoScholar

Engineering Student Trade Journal Articles

**College of Engineering**

Fall 2020

# Using 3D NAND Flash Memory in SSDs to Improve Storage and Performance

**Daniel Welch**

Follow this and additional works at: https://scholar.valpo.edu/stja

Part of the Engineering Commons

This Trade Journal Article is brought to you for free and open access by the College of Engineering at ValpoScholar. It has been accepted for inclusion in Engineering Student Trade Journal Articles by an authorized administrator of ValpoScholar. For more information, please contact a ValpoScholar staff member at scholar@valpo.edu.

## Using 3D NAND Flash Memory in SSDs to Improve Storage and Performance

#### Introduction

In the rapid development process of data storage, 3D NAND is the next generation of this technology in which the semiconductor flash cells of the solid-state drive (SSD) are stacked vertically to increase storage density and read / write efficiency. Originally announced by Toshiba in 2007, but with Samsung creating the first commercially available 3D NAND SSD in 2013, the technology is still extremely new to the market. Despite this, it has already proven to be far more effective and reliable than its 2D NAND counterpart. However, the question remains is it worth the upgrade.

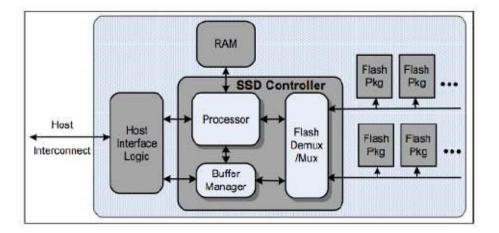

**Figure 1. SSD Logic Components**

#### Architecture

2D NAND flash memory chips consist of thousands of flash blocks that can be further divided into two dimensional arrays of flash cells. These cells each consist of a transistor that stores a charge that comprises the bit of data in the cell. The flash blocks can then be organized into rows called wordlines. In figure 1. above, we can observe the basic layout of a 2D NAND SSD, and to the right of the SSD controller the wordlines are shown. This layout is similar in 3D NAND flash memory chips, however there are a few key differences.

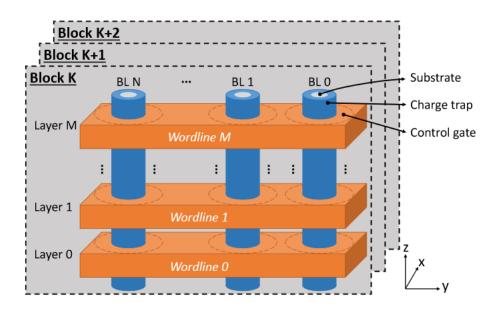

The first change, and the most notable, is the organization of the flash cells. By changing the layout of the flash cell's transistors, the flash blocks are able to stand vertically, forming columns called bitlines (BL) that stand upright out of the wordline. As seen in figure 2, the wordlines still connect the bitlines together to ensure the same efficiency of the read / write speed. In the process of transitioning to multi-level cell (MLC) flash memory, each flash cell is now able to store two bits of data each. By adding a new dimension to the flash blocks and cells, 3D NAND has exponentially increased the storage capabilities of SSDs.

The second difference is the design of the flash cells. Most 2D NAND SSDs feature a floating – gate transistor, which consists of a gate floating in the middle of the transistor, hence the name. This control gate allows voltage into the transistor which can program, read, or write the flash cell. The transistor is then surrounded by an oxide layer to minimize the amount of charge lost. Most 3D NAND designs use charge trap transistors in each flash cell, as opposed to the floating - gate transistors. As shown in figure 2 below, the trap layer wraps around the substrate that makes up the bitline. This allows the layer to maintain the capabilities of the floating – gate transistor, while also acting an insulator for the bitline's substrate. The charge trap layer has caused the control gate to be repositioned, as it now sticks horizontally out of the bitline and merges with the wordline. This rearrangement has ultimately decreased the space used by each flash cell, but at the same time allowing for MLC integration.

Figure 2. Layout of 3D NAND Flash cells

#### **Errors and Solutions**

Flash memory errors occur when the cell voltage is incorrectly changed or read. The chances of these errors occurring exponentially increases in 3D NAND flash memory as the flash cells are manufactured to be closer together. This decreases the reliability of SSDs using this technology, however there are solutions to a large variety of these issues. To decrease the number of errors, SSDs use error-correcting codes (ECC) to find and correct these errors. However, ECC has a limited number of errors it can correct before the data can no longer be fixed, resulting in the end of the SSD's lifetime. ECCs are usable by both 2D NAND as well as 3D NAND SSDs, and usually allow for 10,000+ read / write cycles, which will allow the SSD to last for many years of use.

#### Conclusion

From high-power, industrial computers to standard household office computers, 3D NAND solid state drives will soon be the new standard in non-volatile memory storage. 3D NAND flash memory technology has proven to be cheaper than 2D NAND per gigabyte, faster by 19%, and reduces power consumption with a negligible decrease in reliability. For these reasons, it is most certainly worth the upgrade for the discerning buyer

#### Figure1.

J. Hruska, "How Do SSDs Work?," ExtremeTech, 15, April,2020. [Online]. Available: https://www.extremetech.com/extreme/210492extremetech-explains-how-do-ssds-work. [Accessed: 06-Nov-2020].

#### Figure 2.

Y. Luo, S. Ghose, Y. Cai, E. F. Haratsch, and O.MutLu, "Improving 3D NAND Flash Memory Lifetimeby Tolerating Early Retention Loss and Process Variation," Proc. ACM Meas. Anal. Comput. Syst., 2018